Difference between revisions of "Ethernet packets"

| Line 28: | Line 28: | ||

* Full reset: This resets all chips on the board (except for the FPGA; that should reset only during a power-up) together. This will contain no data. | * Full reset: This resets all chips on the board (except for the FPGA; that should reset only during a power-up) together. This will contain no data. | ||

* Selective reset: This will have flags to reset the Ethernet chip, the ADC, the temperature sensor, and the DAC. Combinations of flags allow a selective reset of any combination of the four chips. This will contain four flags which can be packaged into a single byte. | * Selective reset: This will have flags to reset the Ethernet chip, the ADC, the temperature sensor, and the DAC. Combinations of flags allow a selective reset of any combination of the four chips. This will contain four flags which can be packaged into a single byte. | ||

| − | The first data byte will be an ASCII R: 0x52, 0101 0010. For a full-reset-only design, all remaining bytes in the packet will be padding that the FPGA can ignore. For a selective-reset design, the second data byte will contain the four flags, and all bytes after that will be padding. | + | The first data byte will be an ASCII '''R''': 0x52, 0101 0010. For a full-reset-only design, all remaining bytes in the packet will be padding that the FPGA can ignore. For a selective-reset design, the second data byte will contain the four flags, and all bytes after that will be padding. |

==== "I" packet: initialization complete ==== | ==== "I" packet: initialization complete ==== | ||

| − | This is the acknowledgment packet sent from the FPGA to the PC to state that the reset cycle has been completed and the digital board is ready to resume regular operations. At this point all settings on the digital board have returned to their defaults (likely to mean all DAC channels set to zero). There is no data associated with this packet, so the only significant byte is the first byte, an ASCII I: 0x49, 0100 1001. | + | This is the acknowledgment packet sent from the FPGA to the PC to state that the reset cycle has been completed and the digital board is ready to resume regular operations. At this point all settings on the digital board have returned to their defaults (likely to mean all DAC channels set to zero). There is no data associated with this packet, so the only significant byte is the first byte, an ASCII '''I''': 0x49, 0100 1001. |

=== The query cycle === | === The query cycle === | ||

| Line 39: | Line 39: | ||

==== "Q" packet: query ==== | ==== "Q" packet: query ==== | ||

| + | |||

| + | This is the packet sent from the PC to the FPGA to request a status report. This could be made selective (status of ADC only, status of temperature sensor only, or full status report). However, as the size of an Ethernet packet is so large compared to the amount of data being requested, all data will be sent and the PC can use the data as it desires. Thus there is no data attached to a query packet. The first byte is an ASCII '''Q''': 0x51, 0101 0001. | ||

| + | |||

| + | ==== "S" packet: status report ==== | ||

| + | |||

| + | This is the packet sent from the FPGA to the PC to report on the current status of the board. The first byte of the packet will be an ASCII '''S''': 0x53, 0101 0011. After that will come the status data. | ||

| + | * The first two bytes of data will be the temperature. The temperature sensor returns 10 bits of data. The first byte will contain six leading zeros, then the two MSB of data. The second byte will contain the 8 LSB of data. An alternate scheme would be to convert the 10-bit two's-complement data into 16-bit two's-complement data and return that in two bytes. | ||

| + | * The next 16 bytes of data will be the ADC channels. The ADC returns 8 channels of 12 bits each. The first byte for each channel will have four leading zeros, then the 4 MSB of the data. The second byte for each channel will contain the 8 LSB of the data. The channels will be reported from channel zero to channel seven. An alternate scheme would be to convert the 12-bit two's-complement data into 16-bit two's-complement data and return that in two bytes each. | ||

Revision as of 14:59, 17 July 2007

This page deals with material under development. Please be aware that the information here may change as development proceeds.

This page details the packets we will send across our internal Ethernet to define the standards of communication between the digital boards and the controlling PC. Both the FPGA designer and the PC software programmer will need to make reference to this page in order to coordinate their respective designs.

Open questions

- Will the PC send a layer-2-only packet? Or will the FPGA need to parse out layers 3 and 4?

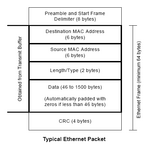

Structure of a packet

To the right is a diagram depicting the structure of an Ethernet packet. On the left side of the diagram is marked the data that will be passed along to the FPGA to be parsed for commands.

To be filled in later

Our packets

We will use six types of packets in our communications, paired into three "conversations" or "cycles": a reset cycle, a query cycle, a programming cycle. Each packet's data section will begin with a single-byte code to identify the packet type. As a mnemonic, these bytes will use ASCII codes to represent a single-letter shorthand for each packet.

The reset cycle

The reset cycle is a conversation whose purpose is to reset the digital control board. On each power-on, the various chips on the digital board need to be re-initialized. This includes the Ethernet chip itself, so the reset functionality needs to be built into the FPGA logic by default and needs to execute on start-up with no external stimulus in order to obtain Ethernet control. However it may also be necessary to instigate a reset externally for some reason. This cycle allows the external PC to initiate a reset and will notify the PC when the system is fully initialized.

"R" packet: reset

This is the packet sent from the PC to the card to initiate a reset process. Two possible reset packet ideas can be considered:

- Full reset: This resets all chips on the board (except for the FPGA; that should reset only during a power-up) together. This will contain no data.

- Selective reset: This will have flags to reset the Ethernet chip, the ADC, the temperature sensor, and the DAC. Combinations of flags allow a selective reset of any combination of the four chips. This will contain four flags which can be packaged into a single byte.

The first data byte will be an ASCII R: 0x52, 0101 0010. For a full-reset-only design, all remaining bytes in the packet will be padding that the FPGA can ignore. For a selective-reset design, the second data byte will contain the four flags, and all bytes after that will be padding.

"I" packet: initialization complete

This is the acknowledgment packet sent from the FPGA to the PC to state that the reset cycle has been completed and the digital board is ready to resume regular operations. At this point all settings on the digital board have returned to their defaults (likely to mean all DAC channels set to zero). There is no data associated with this packet, so the only significant byte is the first byte, an ASCII I: 0x49, 0100 1001.

The query cycle

The query cycle is a conversation regarding the status of the digital board. It polls the sensor devices and reports back their most recent data.

"Q" packet: query

This is the packet sent from the PC to the FPGA to request a status report. This could be made selective (status of ADC only, status of temperature sensor only, or full status report). However, as the size of an Ethernet packet is so large compared to the amount of data being requested, all data will be sent and the PC can use the data as it desires. Thus there is no data attached to a query packet. The first byte is an ASCII Q: 0x51, 0101 0001.

"S" packet: status report

This is the packet sent from the FPGA to the PC to report on the current status of the board. The first byte of the packet will be an ASCII S: 0x53, 0101 0011. After that will come the status data.

- The first two bytes of data will be the temperature. The temperature sensor returns 10 bits of data. The first byte will contain six leading zeros, then the two MSB of data. The second byte will contain the 8 LSB of data. An alternate scheme would be to convert the 10-bit two's-complement data into 16-bit two's-complement data and return that in two bytes.

- The next 16 bytes of data will be the ADC channels. The ADC returns 8 channels of 12 bits each. The first byte for each channel will have four leading zeros, then the 4 MSB of the data. The second byte for each channel will contain the 8 LSB of the data. The channels will be reported from channel zero to channel seven. An alternate scheme would be to convert the 12-bit two's-complement data into 16-bit two's-complement data and return that in two bytes each.